جمع کننده کامل برگشت پذیر با تأخیر کم و کارآمد بر اساس گیت های تافولی

سیده فاطمه دیماد

1

![]() (

گروه مهندسی برق، دانشکده مهندسی 1، دانشگاه آزاد اسلامی واحد شیراز، شیراز، ایران

)

(

گروه مهندسی برق، دانشکده مهندسی 1، دانشگاه آزاد اسلامی واحد شیراز، شیراز، ایران

)

نبی اله شیری

2

(

دانشگاه آزاد اسلامی ، واحد شیراز

)

فرشاد پسران

3

(

دانشگاه آزاد اسلامی، واحد شیراز

)

الکلمات المفتاحية: توان پایین, طراحی برگشت پذیر, جمع کننده بیت نقلی, جمع کننده, سرعت بالا,

ملخص المقالة :

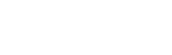

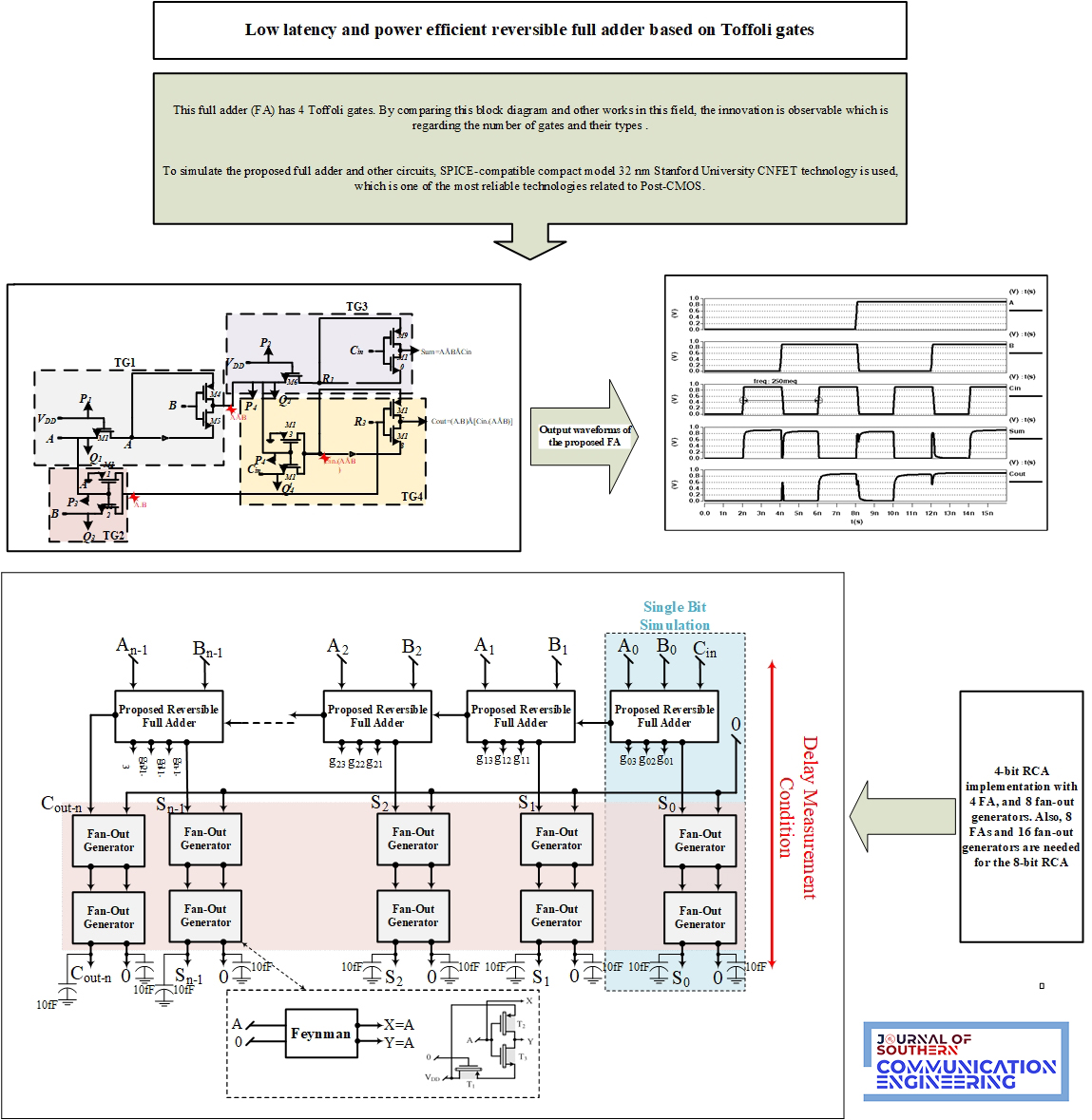

مدارهای برگشت پذیر به دلیل ویژگی های منحصر به فردی که دارند در کاربردهای با قابلیت صرفه جویی در انرژی مفید هستند.از این رو، با استفاده از فناوری ترانزیستور اثر میدانی نانولوله کربنی 32 نانومتری (CNTFET) و با تکیه برگیتهای برگشتپذیر Toffoli، یک مدار تمام جمعکننده جدید ارائه میشود. مدار پیشنهادی دارای 4 گیت اصلی Toffoli و 18 ترانزیستور است. 3 گیت از 4 گیت دارای شماتیک ترانزیستور یکسان با یک ترانزیستور ثابت روشن هستند، اما گیت باقیمانده فقط دو ترانزیستور دارد. مدار پیشنهادی دارای 3 ورودی ثابت و 4 خروجی زائد می باشد. به عنوان یک روش جدید، در مدار پیشنهادی، تنها از یک نوع گیت برگشت پذیر استفاده می شود. نتایج نشان دهنده برتری مدار پیشنهادی از نظر مصرف توان و اتلاف انرژی است. با پیاده سازی مدار پیشنهادی و مدارهای دیگر در جمع کننده زنجیره ای (RCA) 4 بیتی و 8 بیتی، مدار پیشنهادی نسبت به رقیب اصلی به ترتیب 6.83% و 11.25% از نظر توان و انرژی بهبود را نشان می دهد. همچنین در یک RCA با 8 بیت، مدار پیشنهادی 2 درصد نسبت به نزدیکترین رقیب و 27 درصد نسبت به بدترین مدار از نظر توان-تاخیر-سطح مصرفی (PDAP) صرفه جویی دارد. این نتایج مدار طراحی شده را به عنوان یک گزینه مطلوب برای سازه های پیچیده تر با بیت های مرتبه بالا نشان می دهد.

Covering the lack of transistor design of reversible full adders based on CNTFET technology with a channel length of 32 nm.

Design of a new Toffoli gate (TG) and its usage in the proposed full adder for circuitry performance improvement in terms of power and delay.

Use of only one type of reversible gate, Toffoli gate (TG), in the design of the proposed full adder.

Obtaining the proposed full adder with high precision in terms of output voltage generation for use in various high-speed and frequency-dependent applications.

[1] A. Sadeghi, R. Ghasemi, H. Ghasemian and N. Shiri, “High Efficient GDI-CNTFET-Based Approximate Full Adder for Next Generation of Computer Architectures,” IEEE Embedded Systems Letters, vol. 15, no. 1, pp. 33-36, March 2023, doi: 10.1109/LES.2022.3192530.

[2] A. Sadeghi et al., “Voltage over-scaling CNT-based 8-bit multiplier by high-efficient GDI-based counters,” IET Comput. Digit., Tech., vol. 17, pp. 1– 19, Nov. 2023, doi:. 10.1049/cdt2.12049.

[3] N. Shiri, A. Sadeghi, M. Rafiee and M. Bigonah, “SR-GDI CNTFET-based magnitude comparator for new generation of programmable integrated circuits,” Int J Circ Theor., vol. 50, no. 5, pp. 1511- 1536, Apr. 2022, doi: 10.1002/cta.3251.

[4] M. Rafiee, N. Shiri and A. Sadeghi, “High-Performance 1-Bit Full Adder With Excellent Driving Capability for Multistage Structures,” IEEE Embedded Systems Letters, vol. 14, no. 1, pp. 47-50, March 2022, doi: 10.1109/LES.2021.3108474.

[5] M. Sayyaf, A. Ghasemi and R. Hamzehyan, “Design of Low Power Single-Bit Full-Adder Cell Based on Pass-Transistor Logic,” Journal of Southern Communication Engineering, vol. 13, no. 49, pp. 105-112, 2023, doi: 10.30495/jce.2022.692834.

[6] H. Arfavi, S. M. Riazi and R. Hamzehyan, “Evaluation of temperature, Disturbance and Noise Effect in Full Adders Based on GDI Method,” Journal of Southern Communication Engineering, vol. 13, no. 50, pp. 47-66, 2023, doi: 10.30495/jce.2023.1973764.1197.

[7] S. Raveendran, P. J. Edavoor, N. Y. B. Kumar and M. H. Vasantha, “An Approximate Low-Power Lifting Scheme Using Reversible Logic,” in IEEE Access, vol. 8, pp. 183367-183377, 2020, doi: 10.1109/ACCESS.2020.3029149.

[8] M. Haghparast and K. Navi, “A Novel Reversible Full Adder Circuit for Nanotechnology Based Systems,” Journal of Applied Sciences, vol. 7, no. 24, pp. 3995-4000, Dec. 2007, doi: 10.3923/jas.2007.3995.4000.

[9] M .C. Parameshwara and M. Nagabushanam, “Novel low quantum cost reversible logic based full adders for DSP applications,” Int. j. inf. tecnol., no. 13, pp. 1755–1761, Aug. 2021, doi: 10.1007/s41870-021-00762-3.

[10] L. Ni, Z. Guan and W. Zhu , “A general method of constructing the reversible full-adder,” in Proceedings of 3rd International Symposium on Intelligent Information Technology and Security Informatics, Jinggangshan, China, 2010, pp. 109–113, doi: 10.1109/IITSI.2010.25.

[11] M. D. Hafiz, H. Babu, M. D. R. Islam, A. R. Chowdhury and S. M. A. Chowdhury, “On the realization of reversible full-adder circuit,” International Conference on Computer and Information Technology, Dhaka, Bangladesh, 2003, pp. 880-883.

[12] M. Aditya, Y. B. N. Kumar and M. H. Vasantha, “Reversible full/half adder with optimum power dissipation,” 10th International Conference on Intelligent Systems and Control (ISCO), 2016, pp. 1-4, doi: 10.1109/ISCO.2016.7726975.